Description:

This topology agnostic fault detection and location technology is the first such technology that is system-independent, uses only local measurements, and is closed form (non-iterative). Combining these attributes allows this technology to operate quickly to meet the needs of the growing DC microgrid market. This speed advantage bridges a major challenge for DC microgrids by protecting components from speed critical fault events. This technology can also inform the protection needs of high voltage DC lines, which are part of most power systems. Clemson University researchers have developed a fault detection system possessing superior speed and simpler implementation enabling faster protection for component devices as well as determining the location of faults in real time.

Application Stage of Development

Circuit breakers, Converters, TRL 3: Proof of Concept

Faults, DC microgrid,

High voltage, Electrical Engineering

Advantages

- System-independence, which allows for simpler implementation.

- Fast fault detection enabled by using only local measurements with a non-iterative method.

- Controllable fault detection speed by choosing the sampling frequency.

- Usable for any resistance faults, including high resistance faults.

Technical Summary

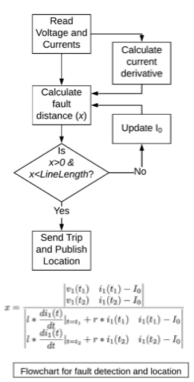

The topology agnostic fault detection and location technique meets speed critical application needs to address current rises that can occur on the order of tens of microseconds in a dc circuit as a result of a fault. When a fault occurs on a feeder-section in a dc microgrid, the current contributions from the dc link capacitors associated with dc-dc converters or ac-dc rectifiers dominate the fault current first. Capacitors resist the rapid change of voltage. So, for a short period of time the capacitor will act like a constant voltage dc source while discharging through the fault. Within this time the current through the dc line will have the same response as it would have for an ideal voltage source instead of the capacitor. So, measurements from this initial period are used to determine the fault location. The method uses only local measurements, preventing delay due to communication. Furthermore, the technique has a fixed execution time due to being non-iterative. System independence allows for a simpler to implement system because the calculation of protection thresholds is based only on the feeder being protected and not on the topology of the whole system. When the rest of the system changes, when an adjacent line is out of operation for example, the thresholds do not have to be recalculated. These features of the technology are conducive to simple and efficient operation to protect vulnerable devices from quickly rising currents during fault events.

View printable PDF version of this technology

____________________________________________________________________________________________

Inventors: Munim Bin Gani

Sukumar Brahma

Patent Type: N/A

Serial Number: 63/242,253

CURF Ref No: 2021-020